MemoryPort Class Reference

Single port of a MemoryInstance. More...

Public Member Functions | |

| def | __init__ (self, str port_name, MemoryPortType type, int bandwidth_min, int bandwidth_max, int|None port_id=None) |

| Collect all the physical memory port related information here. More... | |

| def | add_port_function (self, OperandDirection operand_level_direction) |

| def | port_is_shared_by_two_input_operands (self) |

| def | __str__ (self) |

| def | __repr__ (self) |

| bool | __eq__ (self, Any other) |

| def | __hash__ (self) |

Public Attributes | |

| name | |

| bw_min | |

| bw_max | |

| type | |

| port_id | |

Static Public Attributes | |

| int | port_id_counter = 0 |

Detailed Description

Single port of a MemoryInstance.

Constructor & Destructor Documentation

◆ __init__()

| def __init__ | ( | self, | |

| str | port_name, | ||

| MemoryPortType | type, | ||

| int | bandwidth_min, | ||

| int | bandwidth_max, | ||

| int | None | port_id = None |

||

| ) |

Collect all the physical memory port related information here.

- Parameters

-

port_name bandwidth_min bit/cc bandwidth_max bit/cc type read_only (read), write_only (write), read_write (read_write) port_id port index per memory

Member Function Documentation

◆ __eq__()

| bool __eq__ | ( | self, | |

| Any | other | ||

| ) |

◆ __hash__()

| def __hash__ | ( | self | ) |

◆ __repr__()

| def __repr__ | ( | self | ) |

Here is the call graph for this function:

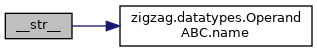

◆ __str__()

| def __str__ | ( | self | ) |

Here is the call graph for this function:

◆ add_port_function()

| def add_port_function | ( | self, | |

| OperandDirection | operand_level_direction | ||

| ) |

◆ port_is_shared_by_two_input_operands()

| def port_is_shared_by_two_input_operands | ( | self | ) |

Member Data Documentation

◆ bw_max

| bw_max |

◆ bw_min

| bw_min |

◆ name

| name |

◆ port_id

| port_id |

◆ port_id_counter

|

static |

◆ type

| type |

The documentation for this class was generated from the following file:

- /home/runner/work/zigzag/zigzag/zigzag/hardware/architecture/memory_port.py