definition of an Analog/Digital In-SRAM-Computing (A/DIMC) core constraint: – activation precision must be in the power of 2. More...

Public Member Functions | |

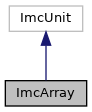

| def | __init__ (self, bool is_analog_imc, int bit_serial_precision, list[int] input_precision, int adc_resolution, int cells_size, float|None cells_area, dict[OADimension, int] dimension_sizes, bool auto_cost_extraction=False) |

| bool | __eq__ (self, Any other) |

| tuple[float, float, float] | get_adc_cost (self) |

| single ADC and analog accumulation cost calculation More... | |

| tuple[float, float, float] | get_dac_cost (self) |

| single DAC cost calculation More... | |

| def | get_area (self) |

| get area of IMC macros (cells, mults, adders, adders_pv, accumulators. More... | |

| def | get_tclk (self) |

| get clock cycle time of imc macros (worst path: dacs -> mults -> adcs -> adders -> accumulators) More... | |

| dict[str, float] | get_peak_energy_single_cycle (self) |

| macro-level one-cycle energy of imc arrays (fully utilization, no weight updating) (components: cells, mults, adders, adders_pv, accumulators. More... | |

| tuple[float, float, float] | get_macro_level_peak_performance (self) |

| macro-level peak performance of imc arrays (fully utilization, no weight updating) More... | |

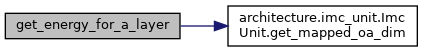

| dict[str, float] | get_energy_for_a_layer (self, LayerNode layer, Mapping mapping) |

| def | __jsonrepr__ (self) |

Detailed Description

definition of an Analog/Digital In-SRAM-Computing (A/DIMC) core constraint: – activation precision must be in the power of 2.

– bit_serial_precision must be in the power of 2.

Constructor & Destructor Documentation

◆ __init__()

| def __init__ | ( | self, | |

| bool | is_analog_imc, | ||

| int | bit_serial_precision, | ||

| list[int] | input_precision, | ||

| int | adc_resolution, | ||

| int | cells_size, | ||

| float | None | cells_area, | ||

| dict[OADimension, int] | dimension_sizes, | ||

| bool | auto_cost_extraction = False |

||

| ) |

Member Function Documentation

◆ __eq__()

| bool __eq__ | ( | self, | |

| Any | other | ||

| ) |

◆ __jsonrepr__()

| def __jsonrepr__ | ( | self | ) |

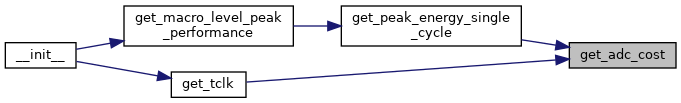

◆ get_adc_cost()

| tuple[float, float, float] get_adc_cost | ( | self | ) |

single ADC and analog accumulation cost calculation

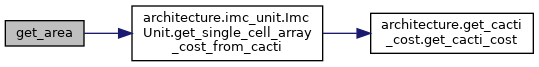

◆ get_area()

| def get_area | ( | self | ) |

get area of IMC macros (cells, mults, adders, adders_pv, accumulators.

Exclude input/output regs)

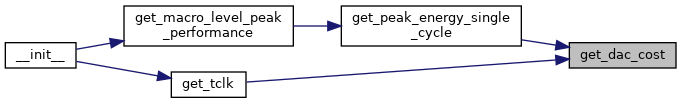

◆ get_dac_cost()

| tuple[float, float, float] get_dac_cost | ( | self | ) |

single DAC cost calculation

◆ get_energy_for_a_layer()

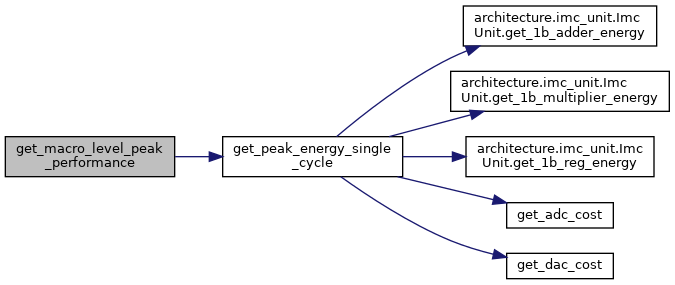

◆ get_macro_level_peak_performance()

| tuple[float, float, float] get_macro_level_peak_performance | ( | self | ) |

macro-level peak performance of imc arrays (fully utilization, no weight updating)

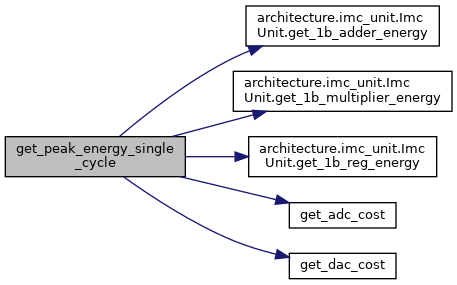

◆ get_peak_energy_single_cycle()

| dict[str, float] get_peak_energy_single_cycle | ( | self | ) |

macro-level one-cycle energy of imc arrays (fully utilization, no weight updating) (components: cells, mults, adders, adders_pv, accumulators.

Not include input/output regs)

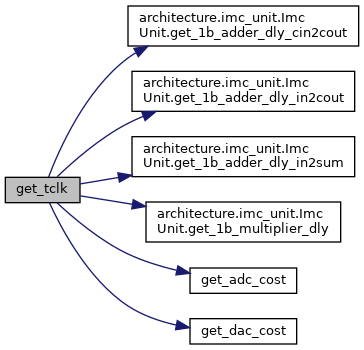

◆ get_tclk()

| def get_tclk | ( | self | ) |

get clock cycle time of imc macros (worst path: dacs -> mults -> adcs -> adders -> accumulators)

Member Data Documentation

◆ activation_precision

| activation_precision |

◆ adc_resolution

| adc_resolution |

◆ area

| area |

◆ area_breakdown

| area_breakdown |

◆ bit_serial_precision

| bit_serial_precision |

◆ cells_area

| cells_area |

◆ cells_size

| cells_size |

◆ cells_w_cost

| cells_w_cost |

◆ dimension_sizes

| dimension_sizes |

◆ energy

| energy |

◆ energy_breakdown

| energy_breakdown |

◆ mapped_rows_total_per_macro

| mapped_rows_total_per_macro |

◆ tclk

| tclk |

◆ tclk_breakdown

| tclk_breakdown |

◆ weight_precision

| weight_precision |

The documentation for this class was generated from the following file:

- /home/runner/work/zigzag/zigzag/zigzag/hardware/architecture/imc_array.py