A single instance within the memory hierarchy, without information about connectivity.

More...

|

| def | __init__ (self, str name, int size, float r_cost=0, float w_cost=0, float area=0, int r_port=1, int w_port=1, int rw_port=0, int latency=1, tuple[MemoryPort,...] ports=tuple(), str mem_type="sram", bool auto_cost_extraction=False, bool double_buffering_support=False, int shared_memory_group_id=-1) |

| | Collect all the basic information of a physical memory module. More...

|

| |

| None | update_size (self, int new_size) |

| | Update the memory size of this instance. More...

|

| |

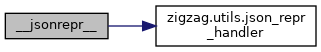

| def | __jsonrepr__ (self) |

| | JSON Representation of this class to save it to a json file. More...

|

| |

| bool | __eq__ (self, object other) |

| |

| def | has_same_performance (self, "MemoryInstance" other) |

| | Wether using this instance will result in the same estimations as using the other instance. More...

|

| |

| def | __hash__ (self) |

| |

| def | __str__ (self) |

| |

| def | __repr__ (self) |

| |

A single instance within the memory hierarchy, without information about connectivity.

◆ __init__()

| def __init__ |

( |

|

self, |

|

|

str |

name, |

|

|

int |

size, |

|

|

float |

r_cost = 0, |

|

|

float |

w_cost = 0, |

|

|

float |

area = 0, |

|

|

int |

r_port = 1, |

|

|

int |

w_port = 1, |

|

|

int |

rw_port = 0, |

|

|

int |

latency = 1, |

|

|

tuple[MemoryPort, ...] |

ports = tuple(), |

|

|

str |

mem_type = "sram", |

|

|

bool |

auto_cost_extraction = False, |

|

|

bool |

double_buffering_support = False, |

|

|

int |

shared_memory_group_id = -1 |

|

) |

| |

Collect all the basic information of a physical memory module.

- Parameters

-

| name | memory module name, e.g. 'SRAM_512KB_BW_16b', 'I_RF'. |

| size | total memory capacity (unit: bit). |

| r_bw/w_bw | memory bandwidth (or word length) (unit: bit/cycle). |

| r_cost/w_cost | memory unit data access energy (unit: pJ/access). |

| area | memory area (unit can be whatever user-defined unit). |

| latency | memory access latency (unit: number of cycles). |

| ports | tuple of MemoryPort instances. |

| mem_type | (str): The type of memory. Used for CACTI cost extraction. |

| auto_cost_extraction | (bool): Automatically extract the read cost, write cost and area using CACTI. |

| double_buffering_support | (bool): Support for double buffering on this memory instance. |

| shared_memory_group_id | used to indicate whether two MemoryInstance instances represent the same, shared memory between two cores (feature used in Stream). |

◆ __eq__()

| bool __eq__ |

( |

|

self, |

|

|

object |

other |

|

) |

| |

◆ __hash__()

◆ __jsonrepr__()

JSON Representation of this class to save it to a json file.

◆ __repr__()

◆ __str__()

◆ has_same_performance()

| def has_same_performance |

( |

|

self, |

|

|

"MemoryInstance" |

other |

|

) |

| |

Wether using this instance will result in the same estimations as using the other instance.

This method differs from eq since it does not consider e.g. the shared_memory_group_id

◆ update_size()

| None update_size |

( |

|

self, |

|

|

int |

new_size |

|

) |

| |

Update the memory size of this instance.

◆ area

◆ double_buffering_support

◆ latency

◆ name

◆ ports

◆ r_cost

◆ shared_memory_group_id

◆ size

◆ w_cost

The documentation for this class was generated from the following file: