Classes | |

| class | CactiConfig |

| Configuration for Cacti. More... | |

Functions | |

| tuple[float, float, float, float] | get_cacti_cost (str cacti_path, float tech_node, str mem_type, float mem_size_in_byte, float bw, str hd_hash="a") |

| extract time, area, r_energy, w_energy cost from cacti 7.0 :param cacti_path: the location of cacti :param tech_node: technology node (directly supported node by CACTI: 0.022, 0.032, 0.045, 0.065, 0.09, 0.18) :param mem_type: memory type (sram or dram) :param mem_size_in_byte: memory size (unit: byte) :param bw: memory IO bitwidth :param hd_hash: input file suffix when generating CACTI input file (useful and in avoid of file conflict for multi-processing simulation) Attention: for CACTI, the minimum mem_size=64B, minimum_rows=32 More... | |

| float | get_w_cost_per_weight_from_cacti (str cacti_path, dict[str, float] tech_param, dict[str, Any] hd_param, dict[str, Any] dimensions) |

Function Documentation

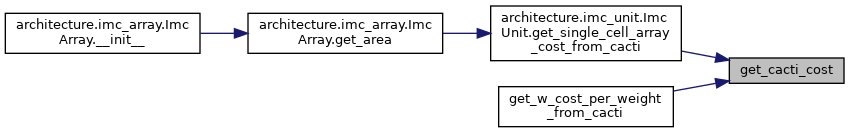

◆ get_cacti_cost()

| tuple[float, float, float, float] architecture.get_cacti_cost.get_cacti_cost | ( | str | cacti_path, |

| float | tech_node, | ||

| str | mem_type, | ||

| float | mem_size_in_byte, | ||

| float | bw, | ||

| str | hd_hash = "a" |

||

| ) |

extract time, area, r_energy, w_energy cost from cacti 7.0 :param cacti_path: the location of cacti :param tech_node: technology node (directly supported node by CACTI: 0.022, 0.032, 0.045, 0.065, 0.09, 0.18) :param mem_type: memory type (sram or dram) :param mem_size_in_byte: memory size (unit: byte) :param bw: memory IO bitwidth :param hd_hash: input file suffix when generating CACTI input file (useful and in avoid of file conflict for multi-processing simulation) Attention: for CACTI, the minimum mem_size=64B, minimum_rows=32

Here is the caller graph for this function:

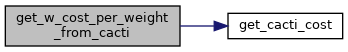

◆ get_w_cost_per_weight_from_cacti()

| float architecture.get_cacti_cost.get_w_cost_per_weight_from_cacti | ( | str | cacti_path, |

| dict[str, float] | tech_param, | ||

| dict[str, Any] | hd_param, | ||

| dict[str, Any] | dimensions | ||

| ) |

Here is the call graph for this function: